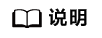

Atlas 200I A2 加速模块SerDes控制器需使用一组外供100MHz差分参考时钟,输入电平类型为CML。

管脚序号 |

加速模块信号名 |

信号方向 |

信号类型 |

信号电平 |

用途/描述 |

|---|---|---|---|---|---|

P120 |

SERDES_CLK0_P |

Input |

- |

800mV~1.2V |

SERDES控制器100MHz参考时钟输入P端。 |

P121 |

SERDES_CLK0_N |

Input |

- |

800mV~1.2V |

SERDES控制器100MHz参考时钟输入N端。 |

关键规格 |

规格要求 |

|---|---|

占空比 |

50%(±5%) |

Trise/Tfall(20%~80%) |

<800ps |

直流偏置电压 |

650mV~750mV |

100MHz差分参考时钟频偏 |

±1MHz(100MHz) |

时钟Buffer时钟源100MHz晶振频偏 |

<50ppm |

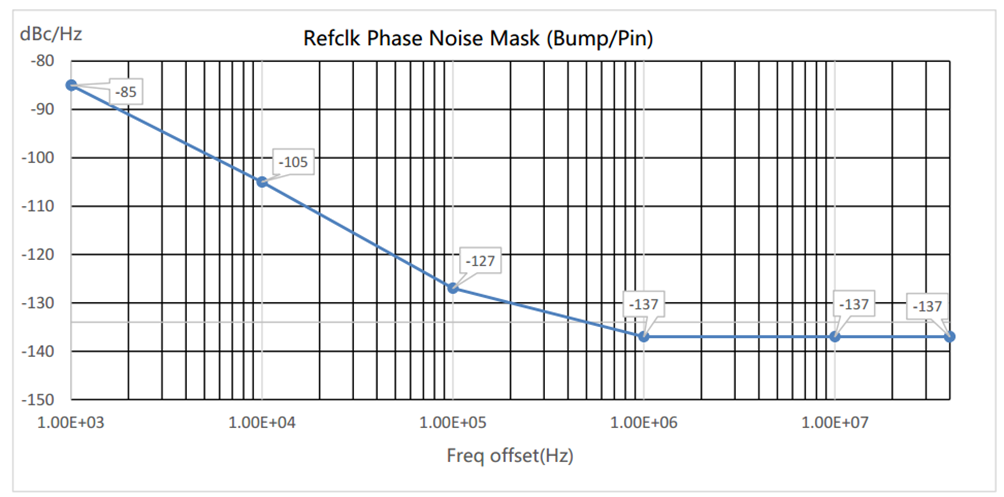

图1 参考时钟相噪指标要求

100MHz参考时钟输入不支持展频。

- 典型应用时钟拓扑(以HCSL电平类型输出为例)

图2 典型应用时钟拓扑图

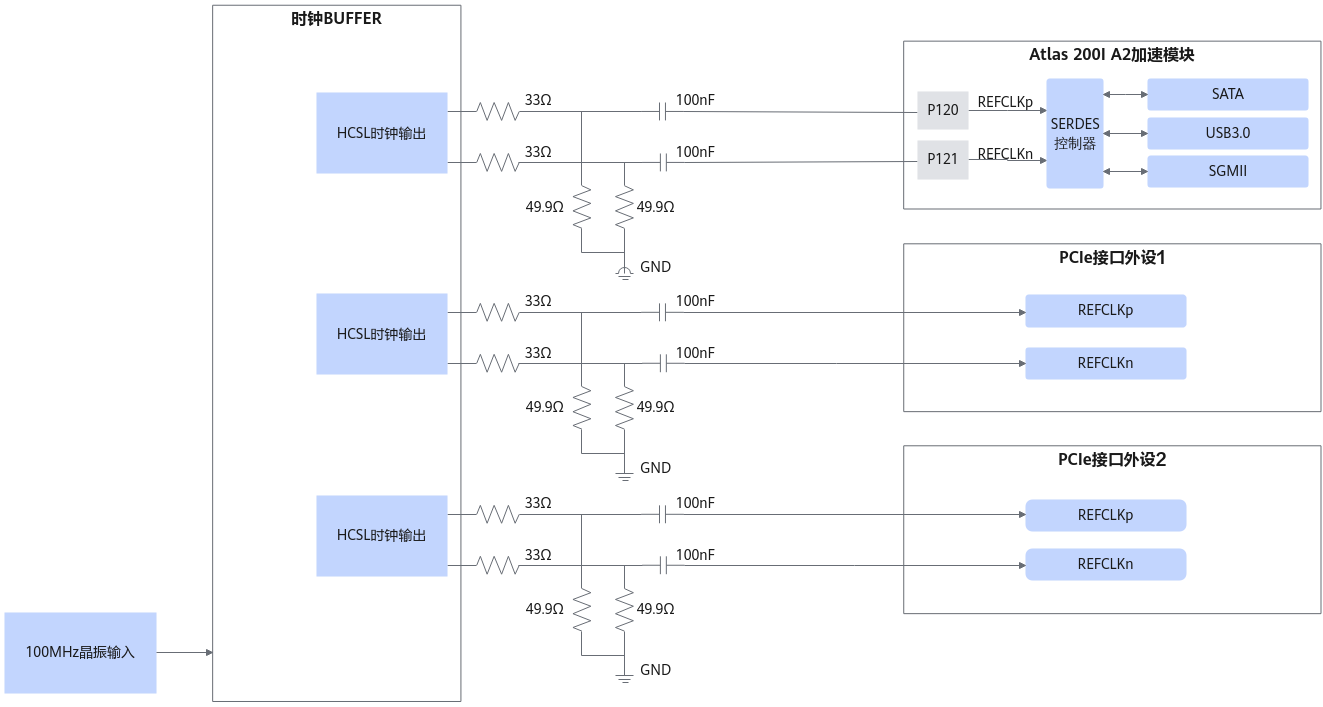

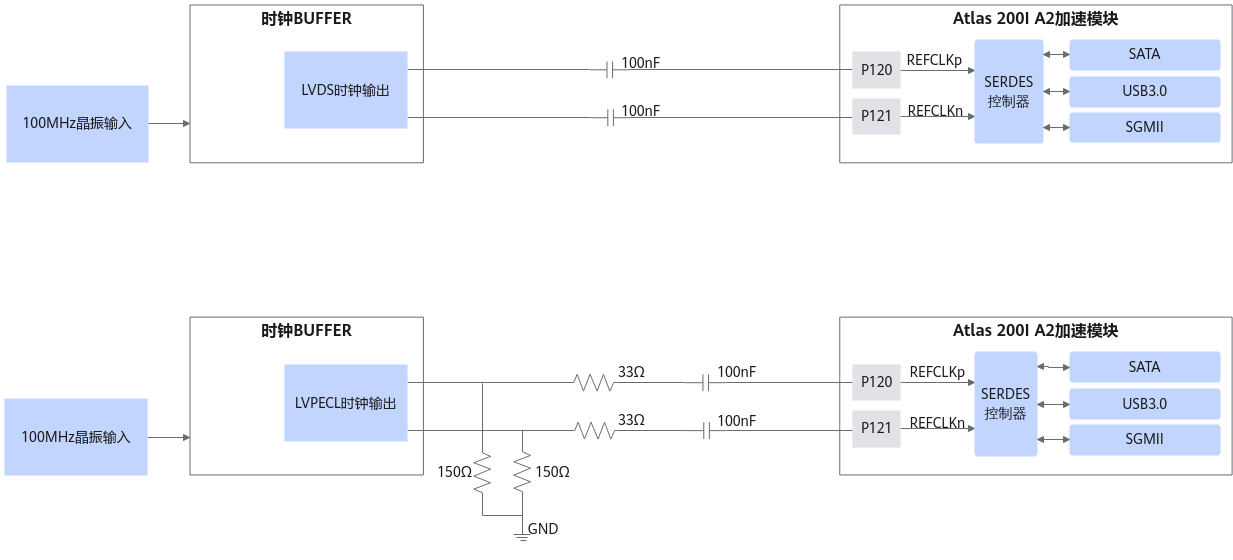

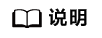

- 常用电平类型匹配电路

图3 常用电平类型匹配电路图

- 100MHz参考时钟需选用AC耦合方式。

- 部分Clock Buffer芯片内部已集成匹配电阻,外部无需增加匹配电阻,选型时请仔细查阅对应芯片的器件手册。

- 时钟Buffer输出电平类型支持LVPECL、HCSL、LVDS,设计时可根据所选电平类型搭建外部匹配电路。