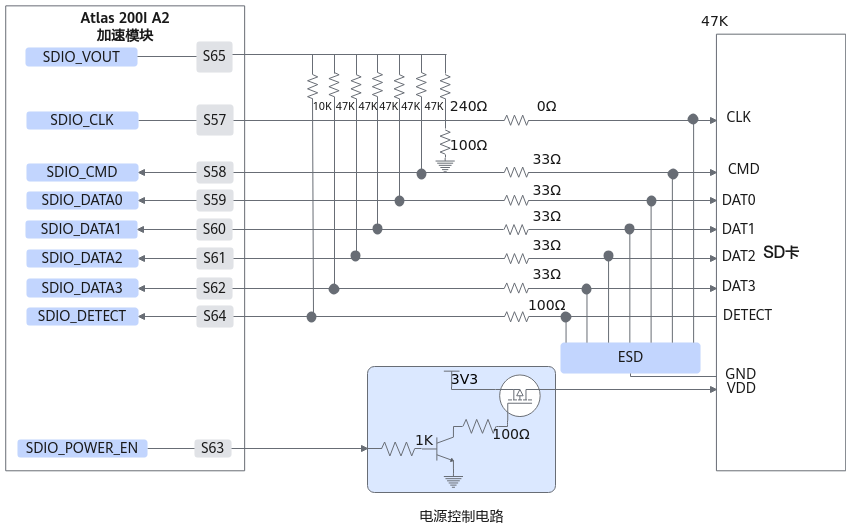

Atlas 200I A2 加速模块上集成了1个SDIO接口,支持对接SDXC卡,向下兼容SDHC卡,支持3.3V/1.8V电平。

管脚序号 |

加速模块信号名 |

信号方向 |

信号类型 |

信号电平 |

用途/描述 |

|---|---|---|---|---|---|

S57 |

SDIO_CLK |

Output |

LVCMOS |

1.8V/3.3V |

SD时钟。 |

S58 |

SDIO_CMD |

Bidirection |

LVCMOS |

1.8V/3.3V |

SD命令。 |

S59 |

SDIO_DATA0 |

Bidirection |

LVCMOS |

1.8V/3.3V |

SD数据通道0。 |

S60 |

SDIO_DATA1 |

Bidirection |

LVCMOS |

1.8V/3.3V |

SD数据通道1。 |

S61 |

SDIO_DATA2 |

Bidirection |

LVCMOS |

1.8V/3.3V |

SD数据通道2。 |

S62 |

SDIO_DATA3 |

Bidirection |

LVCMOS |

1.8V/3.3V |

SD数据通道3。 |

S63 |

SDIO_POWER_EN |

Output |

LVCMOS |

3.3V |

SDIO电源使能控制信号,高电平有效。 |

S64 |

/SDIO_DETECT |

Input |

LVCMOS |

3.3V |

SD卡插入检测信号,低电平有效。 |

S65 |

SDIO_VOUT |

Output |

POWER |

1.8V/3.3V |

SDIO上拉电源输出( 3.3V/1.8V),用于SDIO_CMD/SDIO_DATA[3:0]信号上拉。 |

- 根据环境温度以及可靠性要求,建议使用工业级Micro SD卡。

- Micro SD卡是基于Flash存储介质。当前业界使用较多的是NAND Flash,NAND Flash通过使用Floating Gate存储电子实现数据存储,电子在反复穿过Floating Gate后,会导致Floating Gate存储电子的能力变弱,最终导致击穿而无法存储数据。该特性是NAND Flash的通病,因此在使用NAND Flash时,要充分评估应用业务的写入数据量,避免提前写穿导致器件失效。

信号设计要求

Atlas 200I A2 加速模块SDIO接口设计建议参考:《底板电路参考设计》,SDIO_CLK信号需要靠近SD卡侧,增加240Ω上拉至SDIO_OUT,增加100Ω下拉电阻至GND。

关键规格 |

规格要求 |

|---|---|

结电容 |

<3pF( I/O pin to GND) |

Breakdown Voltage |

Breakdown Voltage >6V |

Clamping Voltage |

Clamping Voltage <12V |

SDIO工作模式

Bus Speed Mode |

Max Clock Frequency[MHz] |

Max Bus Speed[MB/s] |

Signal Voltage |

备注 |

|---|---|---|---|---|

Default Speed |

25 |

12.5 |

3.3V |

参见说明。 |

High Speed |

50 |

25 |

3.3V |

|

SDR12 |

25 |

12.5 |

1.8V |

|

SDR25 |

50 |

25 |

1.8V |

|

SDR50 |

100 |

50 |

1.8V |

|

SDR104 |

208 |

104 |

1.8V |

SD卡电压为IO电压和控制器无关,时钟速率和具体的时钟实现方案相关此处仅为协议规范的最大值。