Atlas 200I A2 加速模块提供一个eMMC (Embedded Multi-Media Card)控制器。

接口特点

- 支持速率:eMMC支持的模式为HS400(最高带宽400Mbps)向下兼容:HS200/High Speed DDR/High Speed SDR模式。

- 支持Auto-tuning功能。

- 支持AMBA(AHB/APB)总线接口。

- 支持SDMA/ADMA2方式的DMA传输。

- 支持命令、数据的CRC校验。

管脚序号 |

加速模块信号名 |

信号方向 |

信号类型 |

信号电平 |

用途/描述 |

|---|---|---|---|---|---|

S42 |

EMMC_CLK |

Output |

LVCMOS |

1.8V |

eMMC时钟,须外接10kΩ电阻下拉至GND。 |

S41 |

EMMC_CMD |

Bidirection |

LVCMOS |

1.8V |

eMMC命令信号,建议在eMMC颗粒侧串接33Ω电阻。 |

S38 |

EMMC_DATA0 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据0, 建议在eMMC颗粒侧串接33Ω电阻。 |

S37 |

EMMC_DATA1 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据1,建议在eMMC颗粒侧串接33Ω电阻。 |

S36 |

EMMC_DATA2 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据2,建议在eMMC颗粒侧串接33Ω电阻。 |

S35 |

EMMC_DATA3 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据3,建议在eMMC颗粒侧串接33Ω电阻。 |

S34 |

EMMC_DATA4 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据4,建议在eMMC颗粒侧串接33Ω电阻。 |

S33 |

EMMC_DATA5 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据5,建议在eMMC颗粒侧串接33Ω电阻。 |

S32 |

EMMC_DATA6 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据6,建议在eMMC颗粒侧串接33Ω电阻。 |

S31 |

EMMC_DATA7 |

Bidirection |

LVCMOS |

1.8V |

eMMC数据7,建议在eMMC颗粒侧串接33Ω电阻。 |

S39 |

EMMC_DS |

Input |

LVCMOS |

1.8V |

eMMC HS400模式读方向时钟,建议在eMMC颗粒侧串接0Ω电阻。 |

S43 |

EMMC_POWER_EN |

Output |

LVCMOS |

1.8V |

eMMC颗粒电源使能控制信号,高电平有效,需加下拉电阻,默认eMMC颗粒不上电。 |

S40 |

/EMMC_RESET |

Output |

LVCMOS |

1.8V |

eMMC复位信号,低电平有效。 |

信号设计要求

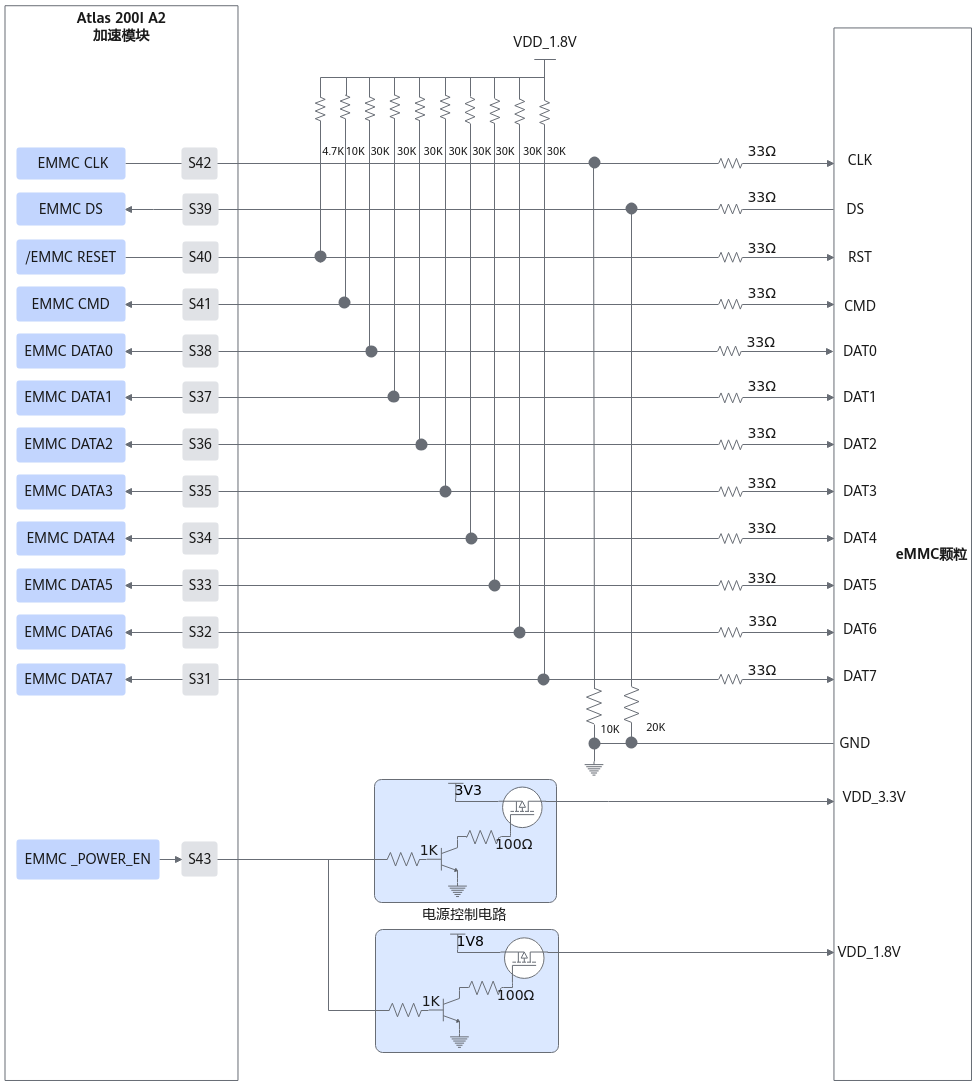

Atlas 200I A2 加速模块eMMC接口设计拓扑:

eMMC工作模式

Bus Speed Mode |

Max Clock Frequency[MHz] |

Max Bus Speed[MB/s] |

Signal Voltage |

备注 |

|---|---|---|---|---|

Backwards Compatibility with legacy MMC card |

26 |

26 |

1.8V |

Backwards Compatibility:1.8V IO电压,1/4/8bit数据位宽,最高26MHz接口时钟。 |

High Speed SDR |

52 |

52 |

1.8V |

High Speed SDR模式: 1.8V IO电压,1/4/8bit数据位宽,最高52MHz接口时钟。 |

High Speed DDR |

52 |

104 |

1.8V |

High Speed DDR模式: 1.8V IO电压,只支持8bit数据位宽,最高52MHz接口时钟。 |

HS200 |

200 |

200 |

1.8V |

HS200模式: 1.8V IO电压,4/8bit数据位宽,最高200MHz接口时钟。 |

HS400 |

200 |

400 |

1.8V |

HS400模式: 1.8V IO电压,8bit数据位宽,最高200MHz接口时钟。 |