AI Core需要把外部存储的数据加载到内部存储中,才能完成相应的计算,对程序员可见的内部存储如表1所示。不同类型的昇腾AI处理器,存储单元大小不同,用户可通过get_soc_spec接口获取。

存储单元 |

描述 |

|---|---|

MTE |

AI Core上有多个MTE(Memory Transfer Engine,存储转换引擎),MTE负责AI Core内部数据在不同Buffer之间的读写管理及一些格式转换的操作,比如填充(padding)、转置(transpose)、3D图像转2D矩阵(Img2Col)等。 |

BIU |

BIU (Bus Interface Unit,总线接口单元), AI Core的“大门”,负责AI Core与总线的交互。BIU是AI Core从外部读取数据以及往外写数据的出入口,负责把AI Core的读写请求转换为总线上的请求并完成协议交互等工作。 |

L1 Buffer |

L1缓冲区,通用内部存储,是AI Core内比较大的一块数据中转区,可暂存AI Core中需要反复使用的一些数据从而减少从总线读写的次数。 某些MTE的数据格式转换功能,要求源数据必须位于L1 Buffer,例如3D图像转2D矩阵(Img2Col)操作。 |

L0A Buffer / L0B Buffer |

Cube指令的输入。 |

L0C Buffer |

Cube指令的输出,但进行累加计算的时候,也是输入的一部分。 |

Unified Buffer |

统一缓冲区,向量和标量计算的输入和输出。 |

Scalar Buffer |

标量计算的通用缓冲区,作为GPR(通用寄存器,General-Purpose Register)不足时的补充。 |

GPR |

通用寄存器(General-Purpose Register),标量计算的输入和输出。 应用开发工程师不需要具体关注这些寄存器,由系统内部实现封装,程序访问Scalar Buffer并执行标量计算的时候,系统内部自动实现Scalar Buffer和GPR之间的同步。 |

SPR |

专用寄存器(Special-Purpose Register),AI Core的一组配置寄存器。 通过修改SPR的内容可以修改AI Core的部分计算行为。 |

本手册将以上AI Core的存储单元分为如下三类:

- Cache:对程序员透明,当指令指定访问下级存储单元的时候,Cache可以对数据进行缓存,从而加快访问速度。

- Buffer:对程序员可见的存储空间,通常用于向量计算或者标量计算中的临时数据保存等。

- Register:对程序员可见的存储空间,通常用于标量计算。

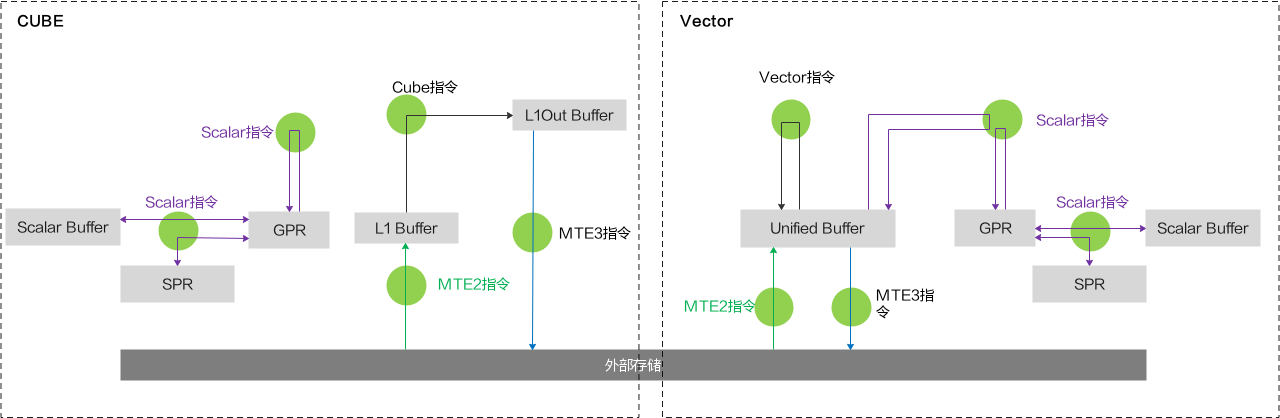

AI Core的每种存储单元只能使用特定的指令访问,当前对程序员开放的存储及指令之间的关系如图1所示。

上图的存储单元是软件层面概念,其中:

- Scalar Buffer对应硬件存储单元Scalar Buffer。

- Unified Buffer对应硬件存储单元Unified Buffer。

- L1 Buffer对应硬件存储单元L1 Buffer。

- L1Out Buffer为抽象出来的存储Cube计算输出数据的存储单元。

由于开发高性能Cube算子难度较大,当前仅支持用户开发Vector算子。