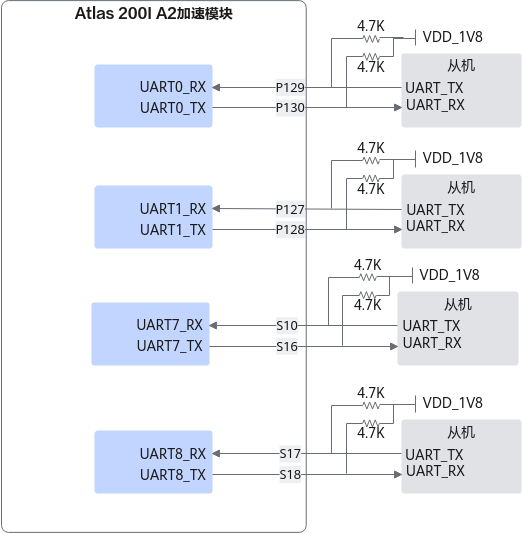

UART接口

UART是Universal Asynchronous Receiver/Transmitter的缩写,即通用异步接收发送器,Atlas 200I A2加速模块可提供7路UART接口,详细复用信息请参考

- 兼容AMBA Specification,支持APB接口,处理总线的读写数据,配置寄存器等。

- 数据位和停止位位宽可配:数据位可配置为5/6/7/8bit,停止位可配置为1/2bit。

- 支持奇、偶校验方式或者无校验位。

- 传输速率编程可配。

- UART2、UART3控制器支持流控。

- UART发送FIFO深度为64bit,宽度为8bit;接收FIFO深度为64bit,宽度为12bit。

- 支持接收FIFO中断、发送FIFO中断、接收超时中断和错误中断可以分别进行屏蔽,产生一个组合中断。

管脚序号 |

加速模块信号名 |

信号方向 |

信号类型 |

信号电平 |

用途/描述 |

|---|---|---|---|---|---|

P129 |

UART0_TX |

Output |

LVCMOS |

1.8V |

UART0发送数据。调试、系统打印、外设扩展等。 |

P130 |

UART0_RX |

Input |

LVCMOS |

1.8V |

UART0接收数据。调试、系统打印、外设扩展等。 |

P127 |

UART1_TX |

Output |

LVCMOS |

1.8V |

UART1发送数据。 |

P128 |

UART1_RX |

Input |

LVCMOS |

1.8V |

UART1接收数据。 |

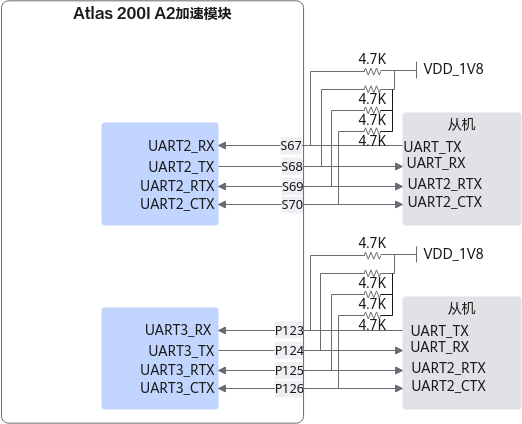

S67 |

UART2_TX |

Output |

LVCMOS |

1.8V |

UART2发送数据。 |

S68 |

UART2_RX |

Input |

LVCMOS |

1.8V |

UART2接收数据。 |

S69 |

/UART2_RTX |

Input |

LVCMOS |

1.8V |

UART2发送请求,硬件流控信号,低电平有效。 |

S70 |

/UART2_CTX |

Output |

LVCMOS |

1.8V |

UART2 发送允许,硬件流控信号,低电平有效。 |

P123 |

UART3_TX |

Output |

LVCMOS |

1.8V |

UART3发送数据。 |

P124 |

UART3_RX |

Input |

LVCMOS |

1.8V |

UART3接收数据。 |

P125 |

/UART3_RTX |

Input |

LVCMOS |

1.8V |

UART3发送请求,硬件流控信号,低电平有效,可复用为UART6_RX。 |

P126 |

/UART3_CTX |

Output |

LVCMOS |

1.8V |

UART3发送允许,硬件流控信号,低电平有效。可复用为UART6_TX。 |

S10 |

I2S0_MCLK |

Output |

LVCMOS |

1.8V |

可复用为UART7_TX,UART7发送数据。 |

S16 |

I2S1_MCLK |

Input |

LVCMOS |

1.8V |

可复用为UART7_RX,UART7接收数据。 |

S17 |

I2S1_BCLK |

Output |

LVCMOS |

1.8V |

可复用为UART8_TX,UART8发送数据。 |

S18 |

I2S1_LRCK |

Input |

LVCMOS |

1.8V |

可复用为UART8_RX,UART8接收数据。 |