PCIE接口

项目 |

设计要求 |

说明 |

|---|---|---|

速率 |

2.5Gbps/5Gbps/8Gbps |

- |

拓扑结构 |

点对点 |

- |

传输线阻抗 |

差分90ohm,±10% |

- |

参考面 |

参考地平面、无跨分割 |

- |

差分对间距 |

建议4H |

H为参考平面介质厚度 |

TX/RX间距要求 |

不同层布线或同层TX/RX差分对之间间距>6H,建议地隔离 |

H为参考平面介质厚度 |

插损要求 |

插损> -15dB@4GHz |

插损要求为模组连接器到对向芯片bump器插损 |

差分对间skew |

|

- |

差分对内等长 |

2mil |

- |

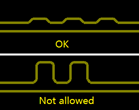

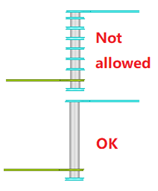

差分对内skew补偿 |

如图 |

|

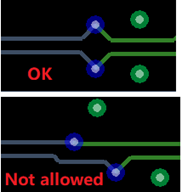

回流地孔 |

换层处添加回流地孔,信号孔对称布局 |

|

过孔数量 |

≤2个 |

- |

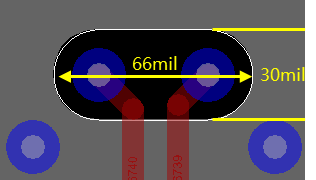

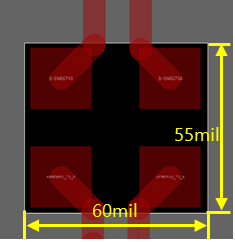

信号过孔阻抗连续性 |

右图为参考板反焊盘尺寸,建议用户根据实际板材和层叠通过仿真确定 |

|

信号过孔STUB长度 |

≤16mil |

|

信号过孔非功能焊盘 |

去除非功能焊盘 |

|

AC耦合电容 |

建议靠近连接器放置,TX、RX都需要放置 |

- |

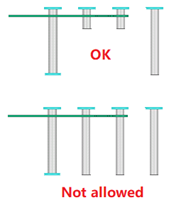

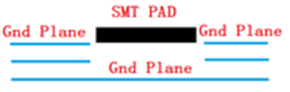

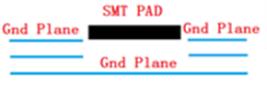

AC耦合电容阻抗连续性 |

右图为参考板优化方式,建议根据层叠,电容封装,板材通过仿真决定 |

参考:0402电容 |

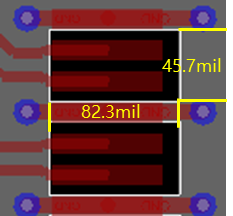

连接器焊盘阻抗连续性 |

右图为参考板优化方式,建议根据层叠,电容封装,板材通过仿真决定 |

|

父主题: PCB设计