TBE算子性能优化

TBE DSL算子

当DSL方式实现的算子性能不满足需求时,可以参考如下流程进行优化:

- 可以借助AOE自动调优工具进行调优,详细操作可参见《AOE工具使用指南》。

- 若调优后仍不满足需求,可以通过DSL算子实现时的一些技巧来进一步优化,可参见DSL性能优化。

TBE TIK算子

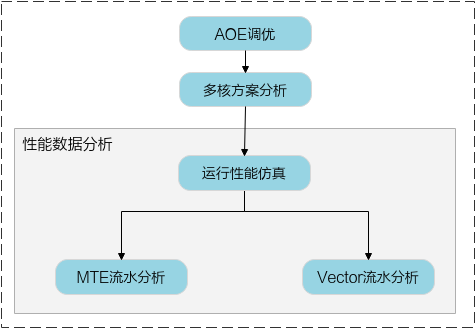

TBE TIK算子性能优化的主要流程如下所示:

图1 TBE TIK算子调优流程

- 首先查看需要优化的算子是否在AOE支持的算子列表中,若支持,则先使用AOE工具对指定算子进行调优。

- 调优后,再对算子进行多核方案的分析,分析算子的多核方案是否合理,是否使能了double buffer,详细分析方法请参见多核与double buffer。

- 使用MindStudio工具对算子进行UT测试,利用UT测试的性能仿真工具展示算子的调度流水线,并进行详细的性能数据分析。

- MTE指令的执行流水线分析。

若MTE1~MTE3指令的执行流水相对于整个时钟周期的占比超过80%,则说明DMA搬移性能较差,此种情况需要重点关注解决。

若MTE指令的执行流水不连续,则说明搬运搬出数据时的并行度不高。

详细可参见计算分片进行优化。

- Vector指令的执行流水线分析。

若Vector指令的执行流水不连续,则说明Vector计算单元未被充分利用,需要审视同步指令的使用情况及指令的并行度。

若Vector指令的执行流水相对于整个时钟周期的占比超过80%,说明当前Vector计算单元已被充分利用,若想继续进行性能提升,需要对指令并行度、算法是否最优等进行审视。

- MTE指令的执行流水线分析。

父主题: 专题